Semiconductors

# Interfacing ISPI I 60x to Fujitsu<sup>®</sup> SPARClite<sup>®</sup> RISC Processor

## Application Note Rev. 1.0

Revision History:

| Rev | Date     | Descriptions   | Author    |

|-----|----------|----------------|-----------|

| 1.0 | Jan 2003 | First release. | Jason Ong |

**Note**: ISP1160x denotes any Philips embedded USB host controller whose name starts with 'ISP1160'; this includes ISP1160A, ISP1160A1, and any future derivatives.

We welcome your feedback. Send it to wired.support@philips.com.

This is a legal agreement between you (either an individual or an entity) and Philips Semiconductors. By accepting this product, you indicate your agreement to the disclaimer specified as follows:

#### DISCLAIMER

PRODUCT IS DEEMED ACCEPTED BY RECIPIENT. THE PRODUCT IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, PHILIPS SEMICONDUCTORS FURTHER DISCLAIMS ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANT ABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NONINFRINGEMENT. THE ENTIRE RISK ARISING OUT OF THE USE OR PERFORMANCE OF THE PRODUCT AND DOCUMENTATION REMAINS WITH THE RECIPIENT. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, IN NO EVENT SHALL PHILIPS SEMICONDUCTORS OR ITS SUPPLIERS BE LIABLE FOR ANY CONSEQUENTIAL, INCIDENTAL, DIRECT, INDIRECT, SPECIAL, PUNITIVE, OR OTHER DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF BUSINESS PROFITS, BUSINESS INTERRUPTION, LOSS OF BUSINESS INFORMATION, OR OTHER PECUNIARY LOSS) ARISING OUT OF THIS AGREEMENT OR THE USE OF OR INABILITY TO USE THE PRODUCT, EVEN IF PHILIPS SEMICONDUCTORS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

### **CONTENTS**

| I.     | OVERVIEW                                             | . 4 |

|--------|------------------------------------------------------|-----|

|        | ISP1160X PROCESSOR INTERFACE SIGNALS                 |     |

| 3.     | FUJITSU SPARCLITE                                    |     |

| 4.     | CONSIDERATIONS IN TIMING DIAGRAMS AND WAIT STATES    | . 5 |

| 5.     | USING INTERRUPTS                                     | . 6 |

| 6.     | SCHEMATIC DIAGRAM                                    | . 7 |

| 7.     | REFERENCES                                           | . 9 |

|        |                                                      |     |

| FI     | GURES                                                |     |

| Figure | 4-1: Programmed Interface Timing (16-bit Read/Write) | . 6 |

The names of actual companies and products mentioned herein may be the trademarks of their respective owners. All other names, products, and trademarks are the property of their respective owners.

**Note**: ISP1160x denotes any Philips embedded USB host controller whose name starts with 'ISP1160'; this includes ISP1160A, ISP1160A1, and any future derivatives.

#### I. Overview

When the ISPI160x is integrated into a personal digital assistant (PDA) or handheld personal computer (HPC), it is usually connected to the external bus interface of a Reduced Instruction Set Computer (RISC) processor. This application note presents some of the important issues in such a design, using a concrete example of the Fujitsu SPARClite RISC.

#### 2. ISPI160x Processor Interface Signals

The processor bus interface of the ISPI160x is designed for a simple direct connection with a RISC processor. The data transfer can be done in the programmed I/O (PIO) or direct memory access (DMA) mode. The estimated maximum data transfer rate on the generic processor bus of the ISPI160x is approximately 15 Mbyte/s. This is based on an ISPI160x internal clock frequency value of 48 MHz. To achieve the maximum data transfer rate on the host processor bus, the ISPI160x contains a ping pong structured RAM that allows alternative access from the RISC processor or from the internal Host Controller. The Host Controller uses 2 kbytes of the ping memory and 2 kbytes of the pong memory in its allocated memory.

The main ISPI 160x signals to consider when connecting to a Fujitsu SPARClite RISC processor are:

- A 16-bit data bus: (D[15:0]) for the ISP1160x. The ISP1160x is "little endian" compatible.

- An address line (A0), which is necessary for the complete addressing of the ISPI160x internal registers:

- **A0** = **0**—Selects the Data Port of the Host Controller

- A0 = I—Selects the Command Port of the Host Controller

- A  $\overline{\text{CS}}$  line used for selection of the ISP1160x in a certain address range of the host system. This input signal is active LOW.

- $\overline{RD}$  and  $\overline{WR}$  are common read and write signals. These signals are active LOW.

- A set of DMA channel standard control lines: DREQ, DACK and EOT are used. Since the SPARClite

processor does not contain a DMA controller, these signals will not be used in a minimal hardware

implementation.

- An interrupt line INT, which is programmable as active on level or edge and HIGH or LOW.

- The CLKOUT signal has a maximum value of 48 MHz.

- The RESET signal is active LOW.

#### 3. Fujitsu SPARClite

The SPARClite processor is part of the 32-bit RISC Fujitsu family.

The external bus interface of the SPARClite processor is a non-multiplexed address and data bus. It has a bigendian architecture. An internal programmable Chip Select logic and an on-chip address decoder allow easy interfacing to EPROM, DRAM (EDO/FPM), UART, or general ASIC without additional glue logic. The integrated DRAM controller can generate all the signals necessary to provide a direct interface to different types of memory; FPM and EDO DRAMS. The address decoder of the SPARClite processor can generate six programmable Chip Select signals. One of the CS0–CS5 signals will be asserted when the selected address matches the value programmed in the Address Range Specifier Register. The Address Mask Register is used to mask certain bits of the address.

To select the properties of each area, set certain values in the internal control registers:

- Bus size: 8, 16 or 32 bits can be independently set for each area, and is determined by the value of the Bus Width/Cacheable Register of the SPARClite processor.

- Number of wait cycles: can be independently set for each selected area by setting the Wait States Specifier Register of SPARClite.

- Setting the type of space: SRAM, DRAM and EPROM. The SPARClite processor will generate the necessary signals to control any of these types of memory.

Each addressed area of the SPARClite processor can be used only in the big endian mode. For correct data alignment, there must be matching data widths and matching endians. During the design phase of a system using SPARClite and ISPI160x, take extra care when developing schematics and software because the ISPI160x connection requires a 16-bit or little endian configuration of the selected memory area.

#### 4. Considerations in Timing Diagrams and WAIT States

The following is a short study of the timing diagrams of the ISPI 160x.

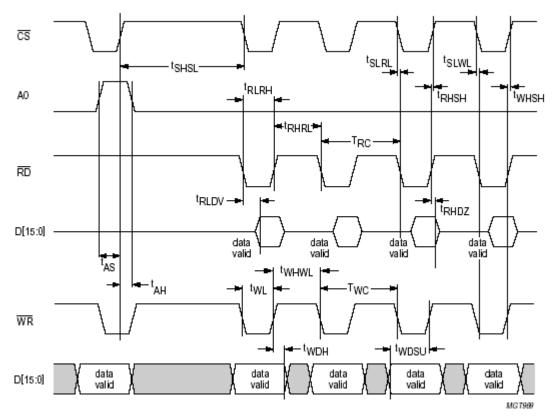

According to the ISPI160x datasheet specifications, a read cycle requires the following main timing parameters (the requirements of the write cycle are similar):

•  $t_{RL}$  = 33 ns ( $\overline{RD}$  LOW pulse width—minimal value required by the ISP1160x),

•  $t_{\text{RHR}} = 110 \text{ ns}$  ( $\overline{\text{RD}}$  HIGH to next  $\overline{\text{RD}}$  LOW—minimal value required by the ISP1160x) and

•  $t_{RHDZ} = 3$  ns ( $\overline{RD}$  hold time, minimal value that can be expected from the ISP1160x).

•  $t_{RC} = 143 \text{ ns}$  (will result as a sum of  $t_{RL}$  and  $t_{RHRL}$ )

•  $t_{SHSL} = 300 \text{ ns}$  (first  $\overline{RD}/\overline{WR}$  after command).

For a detailed analysis of a timing diagram, consider the access of an ISPI I 60x internal register (for example, the Control Register of the Host Controller). It requires two phases: writing the address of the selected register into the Command Port; then only data transfer access (RD/WR) takes place.

The timing diagram in Figure 4-1 describes the two phases of accessing the ISP1160x:

- The first phase is accessing the ISPI160x Command (control) Port of the ISPI160x to write the address (index) of the data port that will be accessed. In this phase,  $\overline{CS}$  is active. The data lines D[15:0] contain the desired address. The  $\overline{WR}$  pulse will be activated and will latch the data. Note the value of  $t_{SHSL}$  that represents the minimum time required between occurrence of the first phase and the second phase. As an example of the Host Controller "Control Register", a value of 01H will be transferred during an  $\overline{RD}$  operation and 81H during a  $\overline{WR}$  operation.

- The second phase consists of the access (read or write) to the data port selected by the address latched in the previous phase. Two timing diagrams are combined again in this second phase: one for the read access and one for the write access. A series of  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  pulses are shown in the diagram to define the timing requirements between two consecutive accesses to the ISPI160:  $t_{\text{RHRL}}$ ,  $t_{\text{WHWL}}$ ,  $t_{\text{RC}}$ ,  $t_{\text{WC}}$ ,  $t_{\text{RLDV}}$ , as specified in the datasheet.

Figure 4-1: Programmed Interface Timing (16-bit Read/Write)

When the ISP1160x connection area is defined as SRAM, ISP1160x will operate correctly when the bus clock CKIO = 33 MHz. Timing measurements show that inserting wait-states in the standard bus cycles of SPARClite is unnecessary. Nevertheless, we will describe wait-state insertion, to cater for cases when faster bus cycles are used for accessing the ISP1160x.

Wait states insertion may be generally achieved using two solutions: hardware or software implementation. Both solutions will delay the rising edge of  $\overline{RD}$  or  $\overline{WR}$  to the next CKIO cycle and will determine an elongation of the  $\overline{RD}$  or  $\overline{WR}$  LOW pulse that can be calculated as:

$t_w = W \times T(CKIO)$ ; where: (W) is the number of wait states desired or selected.

T(CKIO) is the cycle length of CKIO.

**Note**: the value of  $t_{RHRL}$  will not be modified by the number of wait states inserted by any of the solutions mentioned earlier. The value of this parameter must be calculated and correctly adjusted according to the number and length of instructions executed by the SPARClite processor between two successive accesses to the ISPI 160x. The "software solution" for wait-state insertion in a bus cycle is simple and is preferred in a minimal configuration, if additional wait states are necessary.

#### 5. Using Interrupts

The ISPI 160x generates an interrupt on the INT pin. This INT signal can be directly connected to any of the available IRQ signals of the SPARClite processor. The INT of the ISPI 160x can be programmed as active on level or edge and HIGH or LOW, as specified in the *HcHardwareConfiguration Register*.

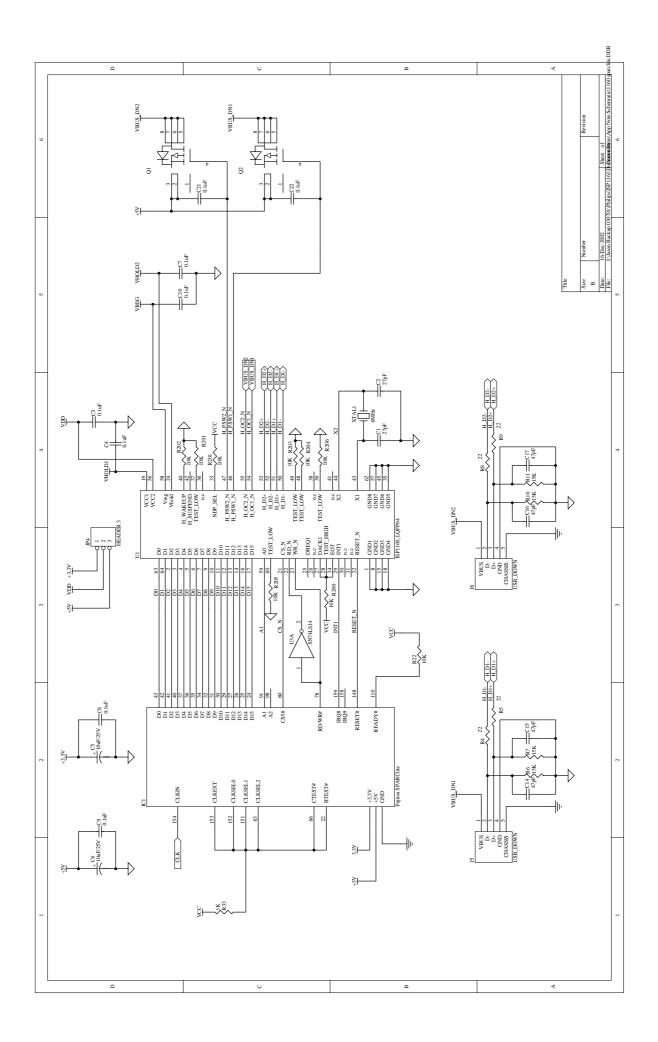

#### 6. Schematic Diagram

The schematic diagram on the following page shows the connection of the ISP1160x to a Fujitsu SPARClite processor in a minimal hardware configuration. For a more detailed description on connecting the ISP1160x to a RISC processor and a study of each category of signals and timing diagrams, refer to the application note *Interfacing ISP1160x* to *Hitachi SH7709 RISC Processor*.

In this configuration, the ISPI 160x is simply selected by CS5#, which is asserted according to the values programmed in the Address Range Specifier Register and the Address Mask Register.

To correctly access the ISP1160x, it is assumed that area 5 is programmed for the SRAM memory type for 16-bit accesses. Data lines D[15:0] of the SPARClite processor will be used in this configuration, and pull-up resistors must be connected to the data bus lines that are not used (D[31:16]); according to the SPARClite datasheet specifications. In this configuration, the  $\overline{\rm RD}$  input signal of the ISP1160x is generated by negating the  $\overline{\rm RD}/\overline{\rm WR}$  signal generated by the SPARClite processor. Therefore, the  $\overline{\rm RD}$  input signal of the ISP1160x will be active most of the time as the SPARClite  $\overline{\rm RD}/\overline{\rm WR}$  signal is HIGH during a read or idle cycle. This will not create any conflicts on the system data bus as the ISP1160x will enable its internal output buffers only when  $\overline{\rm CS}$  is also active in the same time.

Interrupt INT is arbitrarily connected to IRQ8 line of the SPARClite processor. The interrupt controller of the Fujitsu SPARClite processor allows independent setting of the interrupt trigger mode for each input, by programming its *Trigger Mode 0 and 1 Registers*. The ISP1160x also allows programming of polarity (LOW or HIGH) and the signaling mode (level or pulse) for the generated interrupt INT by correctly setting the bits of the *HcHardwareConfiguration* registers.

Input signals  $\overline{\mathrm{H_OC1}}$  and  $\overline{\mathrm{H_OC2}}$  are used by the ISP1160x to detect an overcurrent on the downstream facing ports. Since separate overcurrent detection and protection circuits are implemented for each downstream port in the ISP1160x, detection of overcurrent on a downstream port will cause power to be turned off at that port only. Connecting the voltages of the two downstream ports VBUS\_DN1 and VBUS\_DN2 to the  $\overline{\mathrm{H_OC1}}$  and  $\overline{\mathrm{H_OC2}}$  pins enables detection of the current value by sensing the voltage drop on Q1 and Q2 that are MOS transistors with very low switch-on resistance Rds(on). Q1 or Q2 is selected, depending on the desired maximum current value and this determines the value of Rds(on). For example, if the allowed maximum current is about 0.5 A, a voltage drop of 75 mV will trigger the overcurrent circuitry and an approximate value of Rds(on) = 150 M $\Omega$  will result. Connecting the ISP1160x input pins  $\overline{\mathrm{H_OC1}}$  and  $\overline{\mathrm{H_OC2}}$  to +5 V will disable the internal overcurrent protection of the ISP1160; an external overcurrent protection circuit may also be used.

The RESET input signal of the ISP1160x is connected to the RESET# input signal of the SPARClite processor, and both are connected to the system RESET generation circuitry.

#### 7. References

- Universal Serial Bus Specification Rev. 2.0

- ISPI 160 Embedded Universal Serial Bus Host Controller datasheet

- ISPI 160A1 Embedded Universal Serial Bus Host Controller datasheet

- Interfacing ISPI 160x to Hitachi SH7709 RISC Processor Application Note.

#### **Philips Semiconductors**

Philips Semiconductors is a worldwide company with over 100 sales offices in more than 50 countries. For a complete up-to-date list of our sales offices please e-mail

sales. addresses @www.semiconductors.philips.com.

A complete list will be sent to you automatically.

You can also visit our website

http://www.semiconductors.philips.com/sales/

#### © Koninklijke Philips Electronics N.V. 2003

All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey or imply any license under patent — or other industrial or intellectual property rights.